近年来,随着晶圆级封装技术的不断的提高,众多芯片设计及封测公司开始思考并尝试采用晶圆级封装技术替代传统封装。其中HRP(HeatRe-distribuonPackaging)晶圆级先进封装工艺技术的研究,由深圳市华芯邦科技有限公司(Hotchip)提出,可解决散热、可靠性、成本、器件尺寸等问题,是替代传统封装技术解决方案之一。本文总结了HRP工艺的封装特点和优势,详细的介绍其工艺实现路线,为传统封装技术替代提供解决方案。

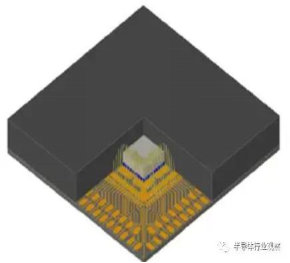

集成电路封装是半导体器件制作的最后一步。传统的芯片封装是指将制作好的晶粒嵌入具有保护作用的塑料、金属或陶瓷壳体中,并与外界电路及其他元器件连接的过程。此过程需要借助银浆或其他胶水将晶粒粘接固定在引线框架上,通过引线键合实现芯片输入输出端口与引线框架引脚实现电气互联,再进行模压塑封、陶瓷烧结或采用金属壳体将晶粒包覆起来,最后进行切割、测试完成芯片封装(如图1)。

a. 芯片内部热量通过硅衬底、导电银浆、引线框架、芯片管脚、焊接锡膏、电路基板进行散热,散热路径 长,热阻高,散热效果一般。

b.芯片内部产生的热量通过电气互联线导热至引线 框架上,再通过引线框架引脚及焊接锡膏导热到电路基板上进行散热。通常电气互联线mil,线径小、路径长,导热能力有限。散热效果一般。

c.芯片产生的热量散发到外壳包封的塑胶、陶瓷或金属包封壳体散热。塑胶包封壳体导热系数低,散热能力差。而陶瓷或金属壳体导热系数较好,但是同时也带来高昂的成本。

为传统芯片封装结构,每颗芯片由几根、几十根甚至上百根键合线实现晶粒与引线框架引脚的电气互联。引线键合工艺因焊线瓷嘴磨损、焊线参数匹配性等因素轻易造成键合线所示)

而塑封材料、晶粒、键合线、引线框架由于不一样的材料热线胀系数不一样,在应用端SMT高温过炉或产品使用的过程中发热,热应力导致键合线受损部位断开,导致器件失效。塑封器件因塑封材料容易吸潮,不同封装材料结合面存在缝隙也轻易造成水汽进入,在SMT工艺及产品使用的过程中,热应力和湿应力的双重作用下将加速器件失效。

芯片封装经过晶粒固定、引线键合、AOI检查、模压、电镀、切割、测试工序,工艺流程长,生产效率慢,需要投入高额的设备成本、人力成本及材料成本,使得产品成本居高不下。

(4)器件尺寸大,阻碍产品微型化问题。芯片封装需要预留足够的引线键合空间,完成引线键合后,还有必要进行塑封,使得器件尺寸远大于晶粒尺寸,对于器件或产品尺寸微型化造成了阻碍。 基于以上传统封装存在的弊端,咱们进行了深入的技术探讨研究,采用HRP晶圆级先进封装技术替代传统封装技术,有效解决产品散热、可靠性、成本、产品尺寸微型化等问题。

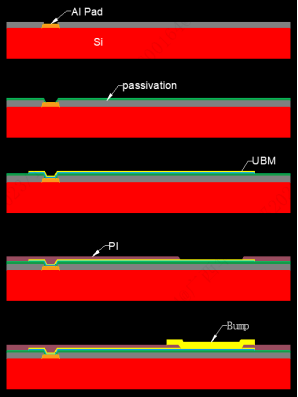

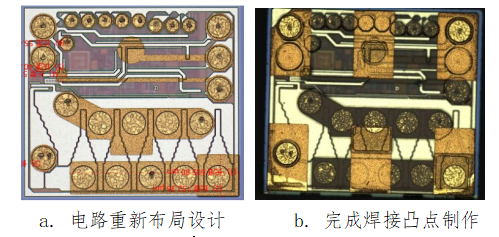

图4 HRP工艺流程图2.1 HRP工艺技术路线 HRP的工艺路线为使用物理气相沉积(PVD)制作UBM层,接着通过光刻、电镀和蚀刻工艺完重构电路布线。 HRP具体的工艺过程

PI绝缘层,作为金属层间绝缘阻隔,在所需制作焊接凸点区域开窗预留凸点制作位置。完成PI层制作后,接着通过UBM层制作、光刻、电镀、蚀刻完成焊接凸点制作,也能够最终靠焊料印刷的方式制作焊接凸点。依据所需要制作的电路层数,不断重复以上步骤就能够得到所需的多层HRP。HRP工艺是在晶圆上进行设计制作,随着所需的HRP完成,芯片的焊接区域也已按照设计所需生成,将晶圆进行划片后即可得到一颗颗的芯。以往的传统封装工艺技术,在完成晶圆划片后,还要进行后到器件级封装,即晶粒固定、引线键合、模压塑封、电镀、切割、测试等工序,才能贴装到PCB板上组装使用。而HRP则无需再进行后道的封装,而是将芯片以倒装(Flip Chip)的方式焊接组装在PCB板上,极大地缩短了互联长度,减小了RC延迟,有效的提升了器件的电性能。

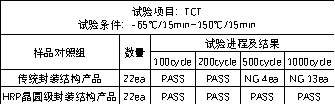

图5 HRP封装结构(1)散热能力好。如图5所示,电路重构设计在芯片表面设计了大面积金属布局,并在特定位置设计较大尺寸的焊接凸点,最终直接倒装焊接在PCB上,其散热路径为直接通过重构电路、焊接凸点、焊接锡膏即可将热量传导到PCB上,且均为大面积的金属导热,导热系数高,散热路径短,从而带来了较好的散热性能。经测试对比,相同芯片,采用HRP晶圆级封装技术替代传统的封装技术,使用的过程中,达到热稳态后,其温度比传统封装产品低40%以上。

(3)成本低。HRP晶圆级封装技术是在晶圆上进行,单片晶圆颗粒数为几千甚至几万颗,UBM生长、光刻、电镀、蚀刻均是正片wafer上所有晶粒一起进行,生产效率非常之高,良率高达99.9%以上,单位生产所带来的成本低。同时HRP线路重构可采用钯、铜等金属制作,使用的材料较少,材料费用低。晶圆完成划片后即可贴装到PCB板上进行组装使用,不再进行后道器件级封装,省去全部的后道工艺制作。经测算,采用HRP晶圆级封装技术综合成本比传统封装技术低30%以上。

(4)产品尺寸微型化。HRP晶圆级封装技术在晶粒上进行电路重构及焊接凸点制作,相比传统封装尺寸因引线键合及塑封额外增加了大量的尺寸空间,采用HRP晶圆级封装技术完成封装后的芯片,其尺寸与裸晶粒完全相同,不会额外增加尺寸,对于追求产品尺寸微型化的应用是最优的解决方案。

、存储器等领域。 目前,大多数芯片采用的封装方式因散热能力不够而或多或少的存在一些可靠性方面的问题。在持续的进行高功率输出时,芯片容易过热进而触发保护机制,导致性能中断,严重影响使用者真实的体验。未解决这样一些问题,HotChip HRP封装技术进行了深入研究,并从底层传热学逻辑出发,全面分析了元器件在工作状态下的界面热阻。研发团队运用有限元

仿真技术,构建了元器件的传热模型,以便改善散热问题。通过对传热模型的研究,HotChip改善了现有的封装方式,提高了芯片的散热性能,保证了可靠性,从而有效地提升了用户的使用体验。4 结束语如今,随着芯片成本日渐上涨以及封装难度的增加,HRP工艺路线将会逐渐在先进封装领域中大放光彩,主要的优势为:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。举报投诉

Wafer Level Package Technology Board Mounting Application Note

(WLP)就是在其上已经有某些电路微结构(好比古董)的晶片(好比座垫)与另一块经腐蚀带有空腔的晶片(好比玻璃罩)用化学键结合在一起。在这些电路微结构体的上面就形成了一个带有

固态图像传感器要求在环境大气中得到一定效果防护。第一代图像传感器安装在带玻璃盖的标准半导体

能使裸片得到很好的密封和异常坚固的保护,但体积比较庞大,制造成本也比较高。引入

随着集成电路设计师将更复杂的功能嵌入更狭小的空间,异构集成包括器件的3D堆叠已成为混合与连接各种功能

; 49 bumps; 3.29×3.29×0.54mm(包括背面涂层)

【Vision Board创客营连载体验】RA8D1-Vision Board上OSPI-Flash实践

1.在线沟通需求

2.报价及方案设计

3.合作及生产

4.现场安装调试

5.人员培训

6.售后支持

Copyright © 2022 半岛体育平台下载-半岛电竞游戏官方app—冰屏、透明LED显示屏、晶膜屏、贴膜屏,自主研发/生产/销售/服务 备案号:粤ICP备19012069号